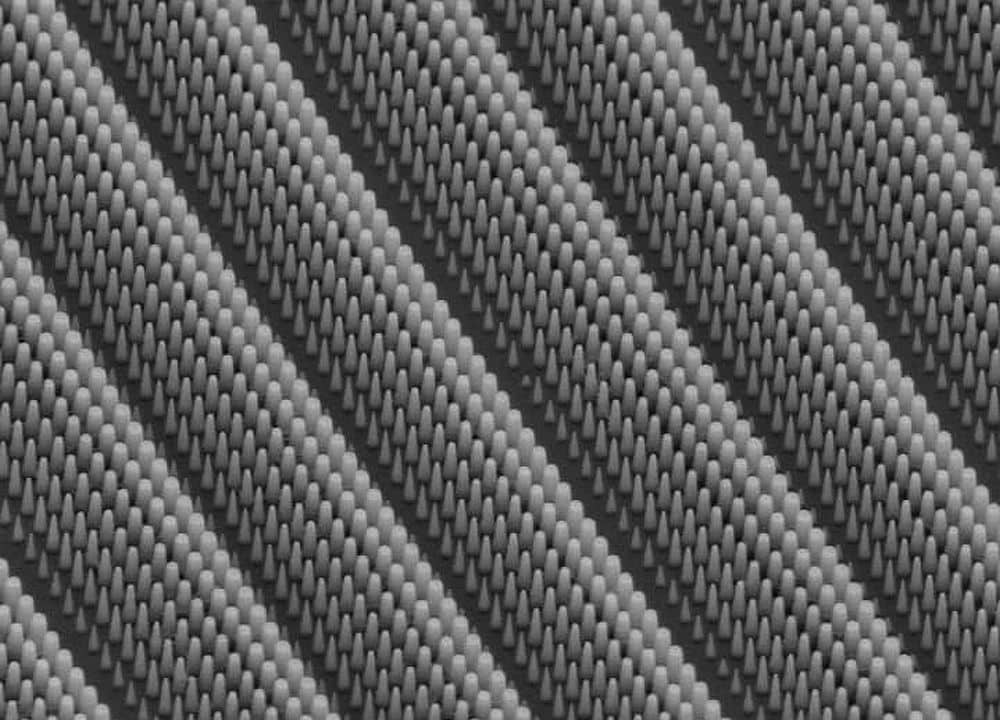

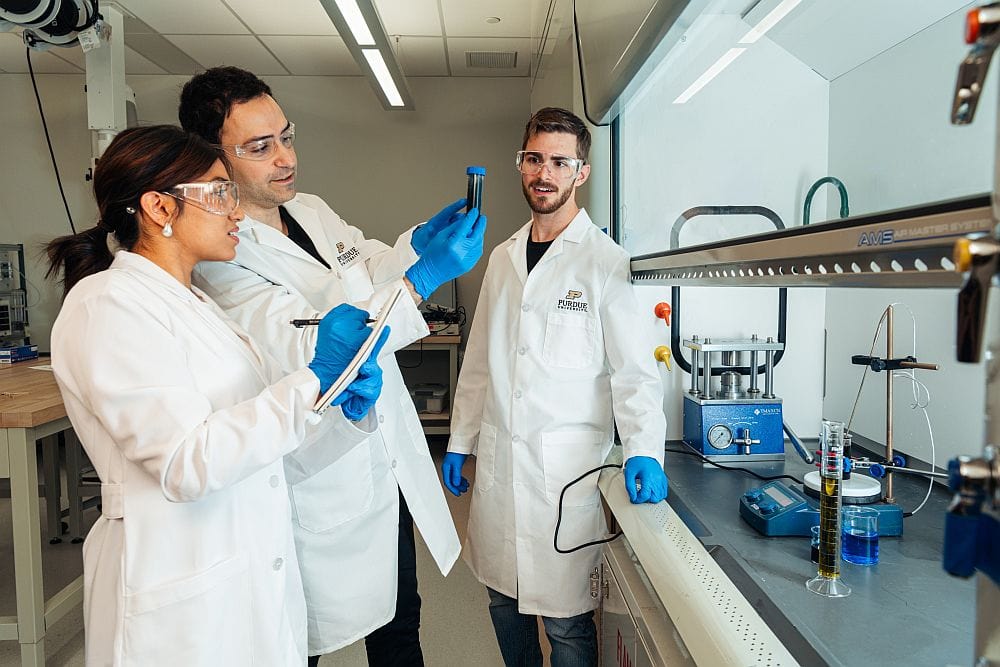

Researchers at Polytechnic University (Hong Kong) demonstrated that sandwiching a simple layer of silver nanoparticles can significantly improve the performance of transistors found in consumer electronics. The findings were published in Applied Physics Letters.

Paddy Chan Kwok-leung, assistant professor of the department of mechanical engineering, and his co-researchers found that the thickness of the nanoparticle layer changes the memory device performance in a more predictable way, thereby optimizing transistor performance to meet application requirements.

According to a PolyU press release, transistors made with a 1-nanometer particle layer have stable memory which lasts for three hours, making it suitable for memory buffers. Transistors with a 5-nanometer-thick layer can retain their charge for a much longer time.

With the appropriate use of nanotechnology, the performance of transistors can be improved and their size can be made thinner. The technology is compatible with the low-cost, continuous roll-to-roll fabrication techniques used to make electronics.

Because of its flexibility and low cost of manufacturing, the researchers anticipate the technology adopted for use in memory devices.

CTT Categories

- Electronics

- Nanomaterials